技術解説 アナログ差動アンプゼロ調整回路

実用アナログ回路

アナログ差動アンプゼロ調整回路

前回は、ホールセンサのバイアス回路を紹介し、アナログセンサの個体差や外乱影響などによる特性変動を抑制する方法を紹介しました。

今回は、センサ信号を増幅するアンプ回路の高精度化について説明します。

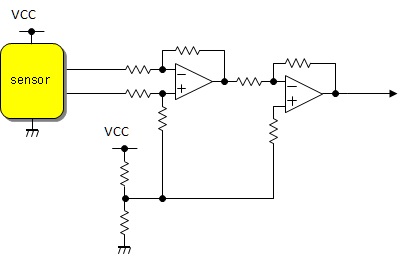

基本差動増幅(センサアンプ)回路

下記に標準的なアナログセンサの差動増幅(アンプ)回路を示します。

この回路の増幅率(ゲイン)は、初段アンプのゲインと後段アンプのゲインの積算となり、比較的高いゲインの回路構成です。Vref動作点は、抵抗分圧器で作る1/2VCCとしています。

この回路の欠点

1/2Vccとしている回路のVref(DC動作点:ゼロバイアス点)基準電位が、実際の回路を構成した場合、各部品のバラツキによってズレる欠点を持ちます。

- センサ個体が持つオフセットによる中点電位ズレ

- オペアンプ個体の入力オフセット

アンプゲインが小さければ、影響度は少ないのですが、一般的に×1000倍(60dB)クラスのゲインとする事が一般的なので例えば、オフセットズレ量が+1mVだとしても、出力に1000倍の+1Vのオフセットを生じてしまいます。

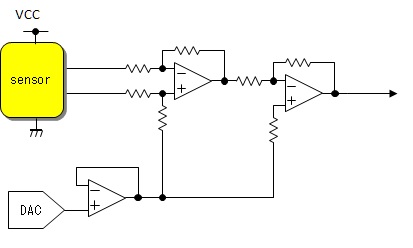

精度を改善するセンサアンプ回路

標準回路のVref電位生成箇所をDACとアナログバッファで構成します。

この回路の特長は、回路に電源投入した際、初期調整としてアンプ出力の電圧を測定しながら、1/2Vccになる様にDACをスキャン変化させます。

この方法で、センサ部品、オペアンプ部品各々の個体差によるオフセットを総合的にキャンセルする事が可能になり、製品個体差を抑制することができます。